# ALPIDE Operations Manual

ALICE ITS ALPIDE development team  $\,$

July 25, 2016 Version: 0.3 Status: DRAFT

# Contents

| 1 | Intr           | oducti  | ion                                                                       | 7  |

|---|----------------|---------|---------------------------------------------------------------------------|----|

| 2 | ALI            | PIDE (  | data sheet                                                                | 10 |

|   | 2.1            | Block   | diagrams                                                                  | 10 |

|   | 2.2            | Interfa | ace signals                                                               | 10 |

|   | 2.3            | Supply  | y, ground and bias nets                                                   | 14 |

|   | 2.4            | Recon   | nmended operating conditions                                              | 15 |

|   | 2.5            | Electr  | ical characteristics                                                      | 16 |

|   | 2.6            | Pad ta  | ables, geometrical data, alignment markers                                | 17 |

| 3 | $\mathbf{Use}$ | r man   | ual                                                                       | 29 |

|   | 3.1            | Contro  | ol interface and protocol                                                 | 30 |

|   |                | 3.1.1   | Chip identification and geographical address allocation                   | 30 |

|   |                | 3.1.2   | Control interfaces                                                        | 31 |

|   |                | 3.1.3   | Control transactions format                                               | 32 |

|   |                | 3.1.4   | Bus turnaround and reply phase of read control transactions $\dots \dots$ | 34 |

|   | 3.2            | Contro  | ol registers and addressing space                                         | 35 |

|   |                | 3.2.1   | Addressing space                                                          | 35 |

|   |                | 3.2.2   | Periphery Control Registers                                               | 36 |

|   |                | 3.2.3   | Region Control Registers and direct access to the DPRAM memories          | 46 |

|   |                | 3.2.4   | Pixel Control Registers                                                   | 48 |

|   |                | 3.2.5   | DACs and Monitoring Control Registers                                     | 50 |

|   |                | 3.2.6   | Test and Debug Control Registers                                          | 54 |

|   | 3.3            | Trigge  | ering and Framing                                                         | 56 |

|   |                | 3.3.1   | Readout Modes                                                             | 57 |

|   |                | 3.3.2   | Frame Timestamping using Bunch Crossing Counter                           | 57 |

|   |                | 3.3.3   | Matrix Memory Bank Masking                                                | 58 |

|   |                | 3.3.4   | STROBE Window Duration                                                    | 58 |

|   |                | 3.3.5   | STROBE Window Extendability                                               | 58 |

|   |                | 3.3.6   | Internal Sequencer                                                        | 59 |

|   |                | 3.3.7   | Triggering and Waveform Diagrams                                          | 59 |

|   | 3.4            | Data '  | Transmission                                                              | 59 |

|   |                | 3.4.1   | Data format and valid data words                                          | 60 |

|      | 3.4.2   | Data format rules                                                                                         | 63 |

|------|---------|-----------------------------------------------------------------------------------------------------------|----|

|      | 3.4.3   | Local Data Bus Sharing Mechanism                                                                          | 63 |

|      | 3.4.4   | Sample Data Streams                                                                                       | 64 |

| 3.5  | Busy S  | State and Conditions                                                                                      | 64 |

|      | 3.5.1   | Signaling of the Busy State                                                                               | 64 |

|      | 3.5.2   | Busy in TRIGGERED Mode                                                                                    | 65 |

|      | 3.5.3   | Busy in CONTINUOUS Mode                                                                                   | 65 |

|      | 3.5.4   | Busy Monitoring                                                                                           | 65 |

|      | 3.5.5   | Busy Testing Functionalities                                                                              | 65 |

|      | 3.5.6   | Busy associated with internal FIFOs and measures to prevent overflow .                                    | 65 |

| 3.6  | Config  | uring pixels for masking and pulsing                                                                      | 66 |

|      | 3.6.1   | Description of PULSE_EN and MASK_EN latches and of the matrix configuration management scheme             | 66 |

|      | 3.6.2   | Control of Column Select and Row Select lines. Control of Pulse gating and propagation of pulsing signals | 69 |

|      | 3.6.3   | Recommended masking and pulsing configuration procedures $\ \ldots \ \ldots$                              | 70 |

|      | 3.6.4   | Notes on Signal Skewing in the context of Pixel Configuration Global Signals                              | 71 |

| 3.7  | Analog  | g test pulse injection and pixel digital testing                                                          | 72 |

|      | 3.7.1   | Generation and timing of pulsing signals                                                                  | 72 |

|      | 3.7.2   | Automatic assertion of an internally generated STROBE following a PULSE command                           | 73 |

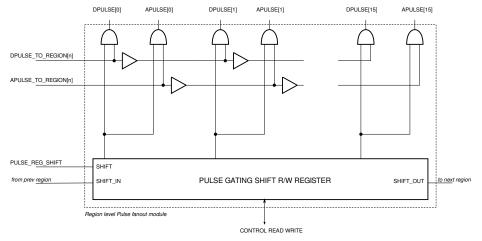

|      | 3.7.3   | Fan-out of pulse signals to the Matrix                                                                    | 73 |

| 3.8  | Chip in | nitialization                                                                                             | 75 |

|      | 3.8.1   | Configuration of in-pixel logic                                                                           | 75 |

|      | 3.8.2   | Configuration and start-up of the Data Transmission Unit                                                  | 75 |

|      | 3.8.3   | Setting up of readout                                                                                     | 75 |

| 3.9  | Data 7  | Transmission Unit and Test Logic                                                                          | 77 |

| 3.10 | Operat  | tion of the ADC                                                                                           | 80 |

|      | 3.10.1  | General settings                                                                                          | 81 |

|      | 3.10.2  | ADC Outputs                                                                                               | 82 |

|      | 3.10.3  | Manual Measurement                                                                                        | 82 |

|      | 3.10.4  | Calibration procedure                                                                                     | 83 |

|      | 3.10.5  | Automatic Measurement                                                                                     | 85 |

| 4            | Pri  | nciples of Operation                               | 87  |

|--------------|------|----------------------------------------------------|-----|

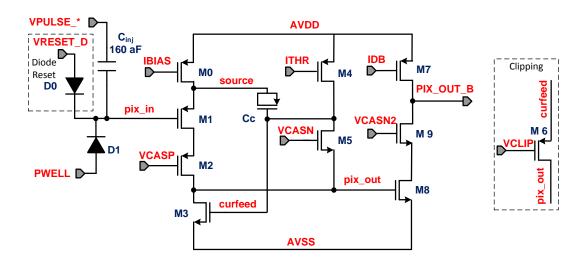

|              | 4.1  | Pixel circuits. Analog Front-End and Digital Pixel | 87  |

|              |      | 4.1.1 Analog Front-End                             | 87  |

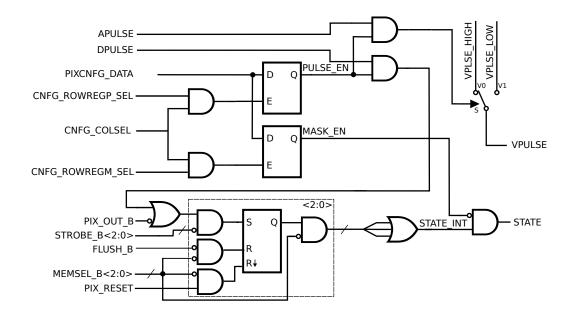

|              |      | 4.1.2 Digital Pixel                                | 88  |

|              | 4.2  | Priority Encoders and pixel indexing               | 88  |

|              | 4.3  | Analog bias and internal DACs                      | 88  |

|              |      | 4.3.1 Monitoring and Overriding of the DACs        | 91  |

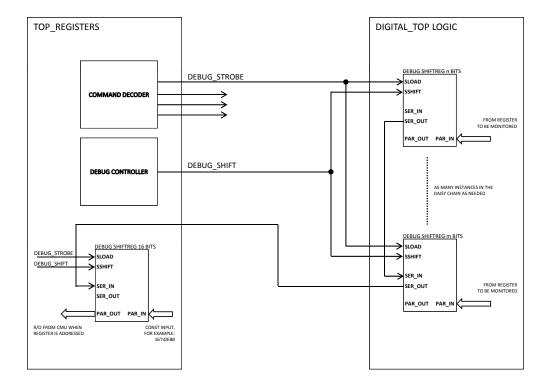

|              | 4.4  | Shadow registers and Debug streams                 | 94  |

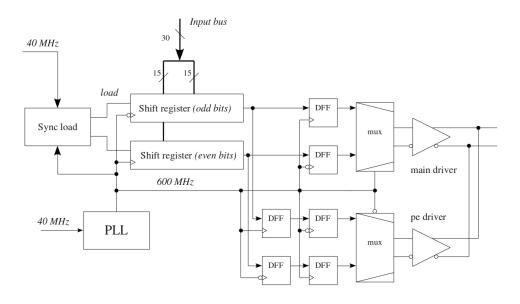

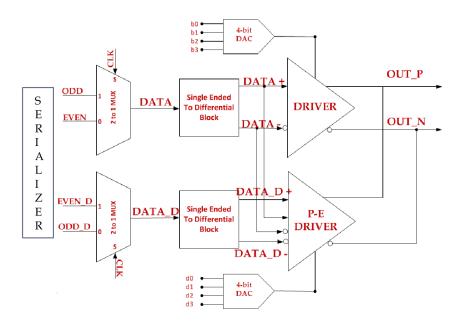

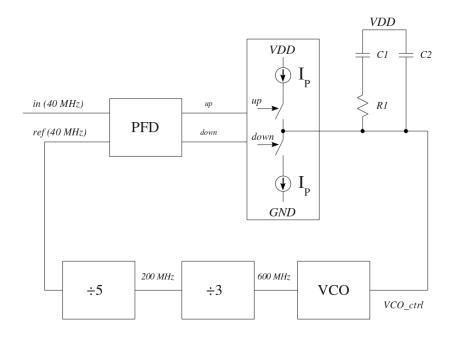

|              | 4.5  | Data Transmission Unit principles of operation     | 98  |

| Aj           | ppen | dices                                              | 103 |

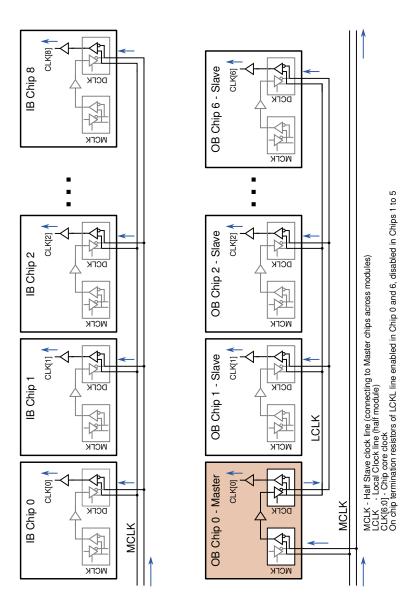

| A            | App  | plication note. Chip and modules clocking schemes  | 104 |

| В            | App  | plication note. ALICE ITS Inner Barrel Modules     | 106 |

| $\mathbf{C}$ | Apr  | olication note. ALICE ITS Outer Barrel Modules     | 108 |

# List of Figures

| 1.1  | General architecture of the ALPIDE chip                                                                                                                                                                  | 8  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of the ALPIDE pixel cell                                                                                                                                                                   | 8  |

| 2.1  | ALPIDE chip block diagram                                                                                                                                                                                | 10 |

| 2.2  | ALPIDE chip block diagram with modules and peripheral hard-blocks                                                                                                                                        | 11 |

| 2.3  | Pinout of the ALPIDE chip                                                                                                                                                                                | 13 |

| 2.4  | ALPIDE pad naming convention                                                                                                                                                                             | 25 |

| 2.5  | Geometry of type A pad                                                                                                                                                                                   | 26 |

| 2.6  | Geometry of type B pad                                                                                                                                                                                   | 27 |

| 2.7  | Geometry of the alignment markers                                                                                                                                                                        | 28 |

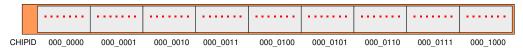

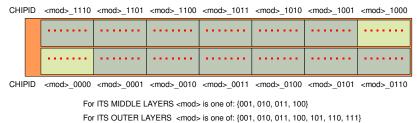

| 3.1  | Illustration of chip identification and geographical address allocation. Default assignments of CHIPID values on one Inner Barrel Module and on a generic Outer Barrel Module                            | 30 |

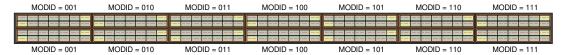

| 3.2  | Illustration of chip identification and geographical address allocation. Default assignments of Module Identifier fields for the Middle Layer Stave and Outer Layer Stave                                | 30 |

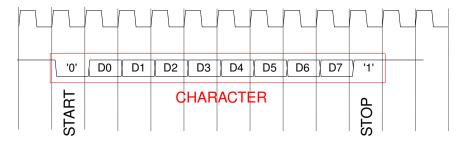

| 3.3  | Format of a single character exchanged on the control bus                                                                                                                                                | 32 |

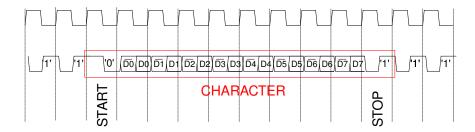

| 3.4  | Format of a single character exchanged on the DCTRL bus with Manchester coding enabled (default)                                                                                                         | 32 |

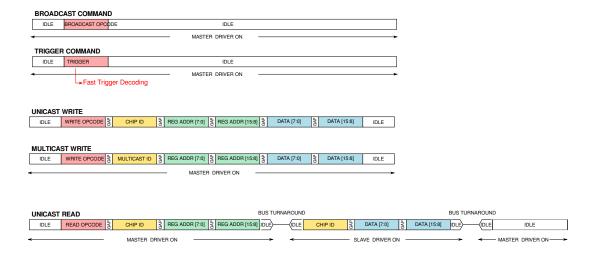

| 3.5  | Format of valid transactions on the control bus                                                                                                                                                          | 34 |

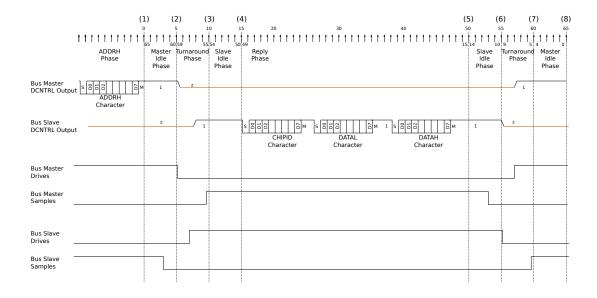

| 3.6  | Timing diagram of the reply phase of a Read transaction including turnaroud phases. Signaling is represented as seen on the differential line at the output of the bus master (off-detector electronics) | 35 |

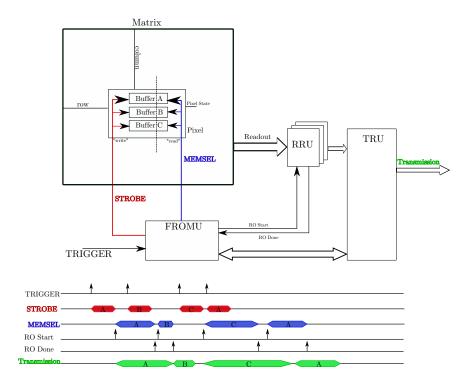

| 3.7  | Pixel MEB Management Scheme                                                                                                                                                                              | 56 |

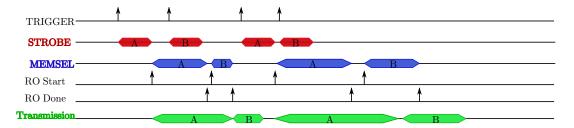

| 3.8  | Pixel MEB Management with Slice C Masked                                                                                                                                                                 | 58 |

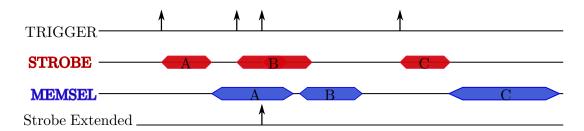

| 3.9  | An illustration of an extended STROBE window followin the reception of a second TRIGGER                                                                                                                  | 59 |

| 3.10 | Internal TRIGGER Sequencer Initiation and Re-Timing                                                                                                                                                      | 59 |

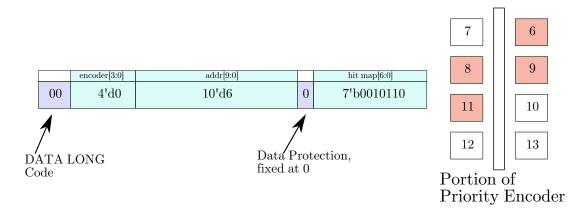

| 3.11 | A depiction of a cluster hit and its DATA LONG representation                                                                                                                                            | 63 |

| 3.12 | A Sample Data Stream on the Local Bus in DDR Mode and the Corresponding Transmission on the Serial Bus                                                                                                   | 64 |

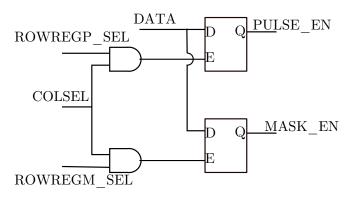

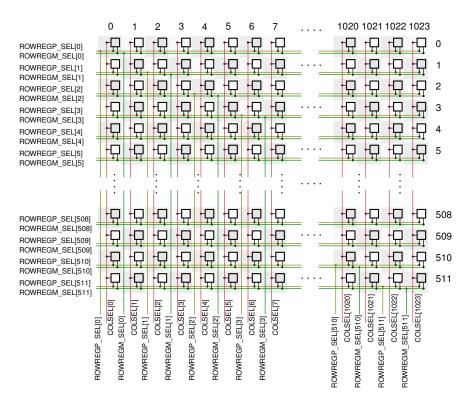

| 3.13 | Schematic of in-pixel latch circuitry                                                                                                                                                                    | 67 |

| 3.14 | Topology of the row and column selection lines to configure the in-pixel Mask and Pulse Enable latches.                                                                                                  | 67 |

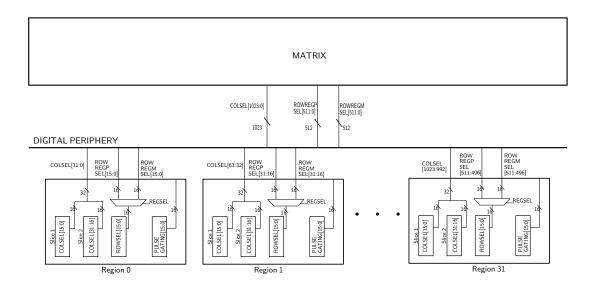

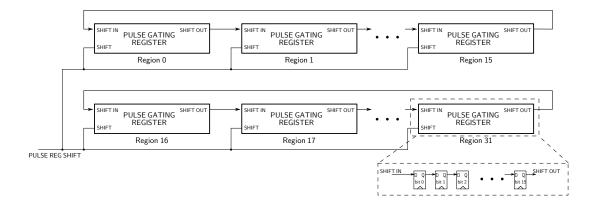

| 3.15 | Scheme of the distribution of the peripheral registers controlling the writing to in-pixel registers and the gating of pulsing signals                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.16 | Illustration of address bus bits used to access pixel configuration registers 69                                                                                                         |

| 3.17 | Address and Data fields of a sample chip control transaction to initialize all Pulse Propagation, Row and Column Select lines to binary 0 70                                             |

| 3.18 | Delay between the assertion of the first bit of the PULSE command and the assertion of the DPULSE as seen by the Matrix                                                                  |

| 3.19 | Fan-out of the Pulsing signals to the Double Columns. Schematic diagram of the circuits in one of the region modules in the periphery, forwarding APULSE and DPULSE to 16 double columns |

| 3.20 | Pulse shift registers scheme where the rotation is triggered on the negative edge of a Test Pulse                                                                                        |

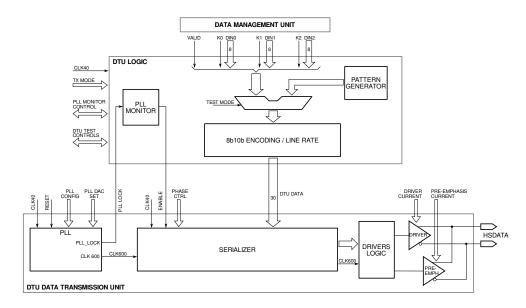

| 3.21 | Functional block diagram of the Data Transmission Unit and the related digital module DTU LOGIC                                                                                          |

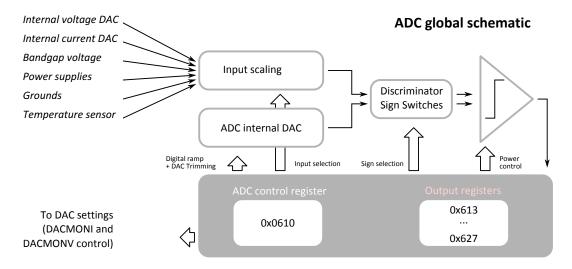

| 3.22 | ADC schematic                                                                                                                                                                            |

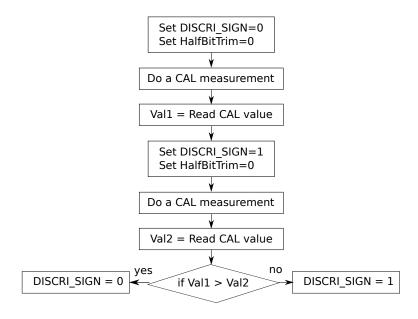

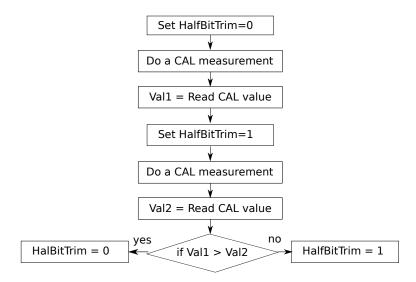

| 3.23 | Calibration 1 : Discriminator sign                                                                                                                                                       |

| 3.24 | Calibration 2 : Half lsb trimming bit                                                                                                                                                    |

| 4.1  | ALPIDE Front-end scheme                                                                                                                                                                  |

| 4.2  | Functional diagram of the pixel logic                                                                                                                                                    |

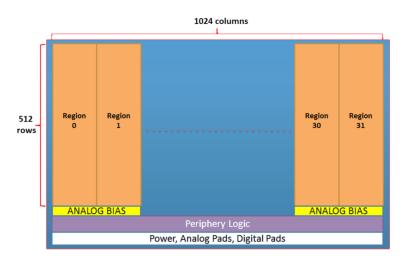

| 4.3  | Region numbering                                                                                                                                                                         |

| 4.4  | Double column numbering inside of a region                                                                                                                                               |

| 4.5  | Indexing of pixels inside a double column provided by the Priority Encoders $91$                                                                                                         |

| 4.6  | DACs scheme                                                                                                                                                                              |

| 4.7  | Current DACs monitoring and overriding scheme                                                                                                                                            |

| 4.8  | Debug Chain Prinicple of Operation                                                                                                                                                       |

| 4.9  | Functional diagram of the Data Transmission Unit                                                                                                                                         |

| 4.10 | Functional diagram of the Data Transmission Unit                                                                                                                                         |

| 4.11 | Simplified schematic of the PLL circuit                                                                                                                                                  |

| A.1  | Illustration of the clock distribution scheme for the ITS Inner Barrel and Outer Barrel Modules                                                                                          |

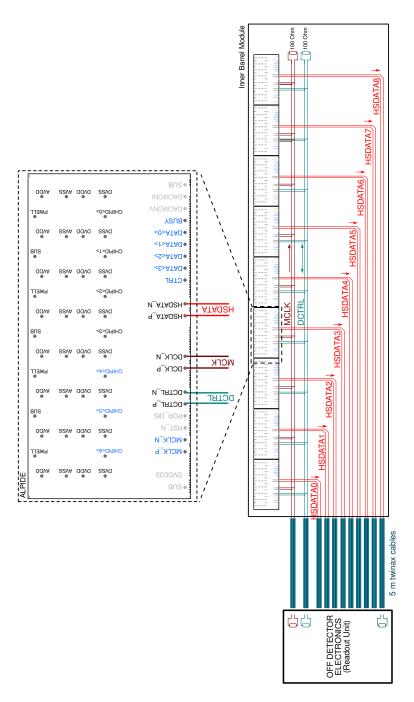

| B.1  | Schematic diagram of the electrical interconnections between the ALICE ITS Upgrade Inner Barrel module and the off-detector electronics                                                  |

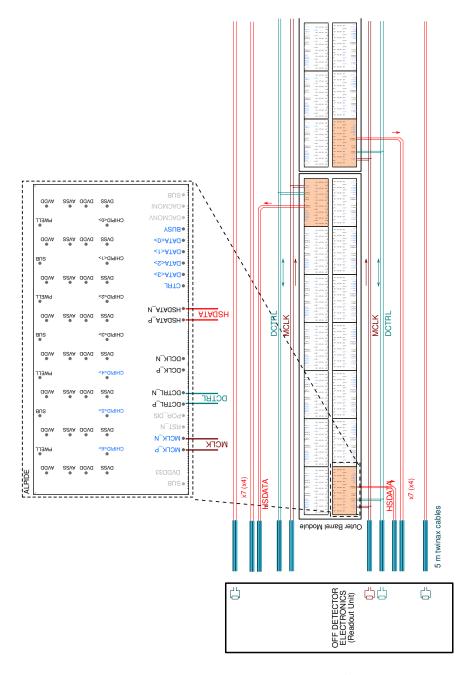

| C.1  | Schematic diagram of the electrical interconnections between ALICE ITS Upgrade Outer Barrel modules and off-detector electronics                                                         |

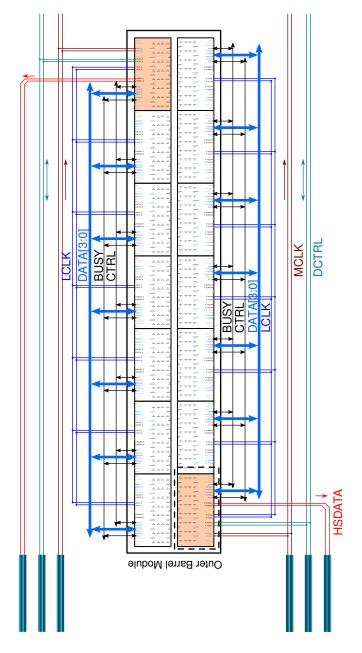

| C.2  | Schematic diagram of the electrical interconnections between ALICE ITS Upgrade Outer Barrel modules and off-detector electronics                                                         |

# 1 Introduction

The ALPIDE chip is a particle detector based on Monolithic Active Pixels and implemented in a 180 nm CMOS technology for Imaging Sensors. It has been designed for the Upgrade of the Inner Tracking System of the ALICE experiment at the CERN Large Hadron Collider.

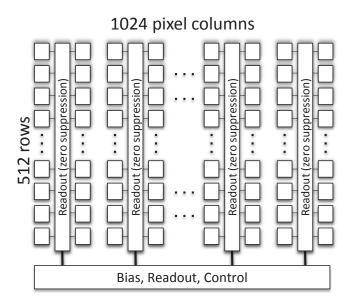

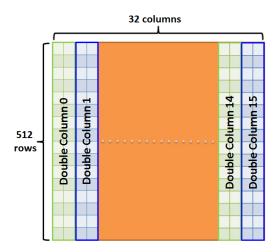

The ALPIDE chip measures 15 mm (Y) by 30 mm (X) and contains a matrix of  $512 \times 1024$  (Y×X) sensitive pixels (Fig. 1.1). The pixels are  $29.24~\mu m \times 26.88~\mu m$  (X×Y). A periphery circuit region of  $1.2 \times 30~mm^2$  including the readout and control functionalities is present. It is assumed that the chip is observed from the circuits side and oriented such that the periphery is at the bottom. The pixel columns are numbered from 0 to 1023 going from left to right. Pixel rows are numbered from 0 to 511 going from the matrix top side downwards to the bottom one immediately above the periphery.

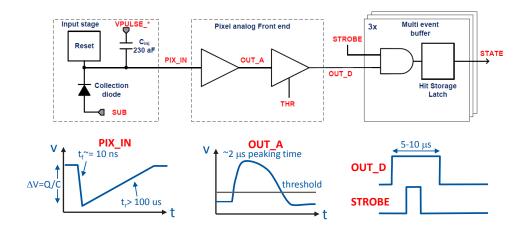

Each pixel cell contains a sensing diode, a front-end amplifying and shaping stage, a discriminator and a digital section (Fig. 1.2). The digital section includes three hit storage registers (Multi Event Buffer), a pixel masking register and pulsing logic.

The front-end and the discriminator are continuously active. They feature a non-linear response and their transistors are biased in weak inversion. Their total power consumption is 40 nW. The output of the front-end has a peaking time of the order of 2  $\mu$ s, while the discriminated pulse has a typical duration of 10  $\mu$ s. The front-end and the discriminator act as an analogue delay line. This allows operating the chip in triggered mode when the latency of the incoming trigger is comparable with the peaking time of the front-end.

A common threshold level is applied to all the pixels. The latching of the discriminated hits in the storage registers is controlled by global STROBE signals. A pixel hit is latched into one of three in-pixel memory cells if a STROBE pulse is applied to the selected cell while the frontend output is above threshold. Three distinct STROBE signals are generated at the periphery and globally applied to all pixels, controlling the storage of the pixel hit information in the pixel event buffers. The generation of the internal STROBE signals can be triggered by an external command (TRIGGER), but it can optionally be initiated by an internal sequencer. The duration of the STROBE pulses is programmable.

In every pixel there is a pulse injection capacitor for injection of test charge in the input of the front-end. A digital-only pulsing mode is also available, forcing the writing of a logic one in the pixel memory cells. The pulsing patterns are fully programmable.

The readout of pixel hit data from the matrix is based on a circuit named Priority Encoder. There are 512 instances of this circuit, one every two pixel columns. The Priority Encoder provides to the periphery the address of the first pixel with a hit in its double column, selecting it according to a hardwired topological priority. During one hit transfer cycle a pixel with a hit is selected, its address is generated and transmitted to the periphery and finally the in-pixel memory element is reset. The address of the next pixel with a hit in the double column is then calculated. This cycle is repeated until the addresses of all pixels initially presenting a valid hit at the inputs of a Priority Encoder have been transmitted to the periphery and all the pixel state registers have been reset. The transfer of the frame data from the matrix to the periphery is therefore zero-suppressed.

Each Priority Encoder is a fully combinatorial circuit and it is steered by sequential logic in the periphery during the readout of a matrix frame. It is implemented in a very narrow region between the pixels, extending vertically over the full height of the columns. There is no free running clock distributed in the matrix and there is no signaling activity if there are no hits to read out. The average energy needed to encode the address of a hit pixel is of

Figure 1.1: General architecture of the ALPIDE chip.

Figure 1.2: Block diagram of the ALPIDE pixel cell.

the order of 100 pJ. Power is consumed proportionally to the readout rate and to the frame occupancy. The Priority Encoders also implement the buffering and distribution of readout and configuration signals to the pixels.

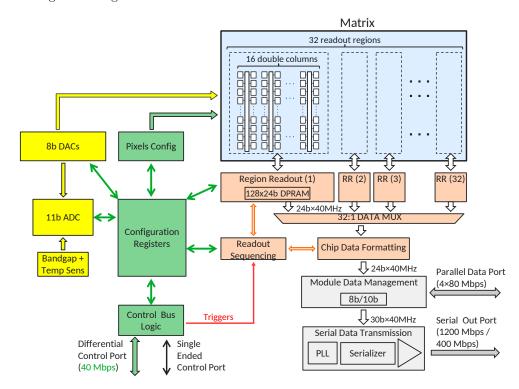

The readout of the matrix is organized in 32 regions ( $512 \times 32$  pixels), each of them with 16 double columns being read out by 16 Priority Encoder circuits (Fig. 2.1). There are 32 corresponding readout modules (Region Readout Units) in the chip periphery, each one executing the readout of a submatrix. The sixteen Double Columns inside each region are read out sequentially, while the thirty-two submatrices are read out in parallel.

The Priority Encoders are driven by state machines in the Region Readout Units. These modules contain de-randomizing memories and perform additional data reduction and formatting. The data from the 32 region readout blocks are assembled and formatted by a Top Readout Unit module. Two major readout modes are supported, one in which the strobing and readout are triggered externally and a second one in which frames are continuously integrated and read out, with programmable duration of the strobe assertion intervals.

Hit data can be transmitted on two different data interfaces according to one of three alternative operating modes envisaged for the application in the Upgraded ALICE ITS: *Inner Barrel chip*, *Outer Barrel Master* and *Outer Barrel Slave*. A 1.2 Gb/s Serial Data port with differential signalling is the largest capacity data readout interface and the primary one for the Inner Barrel Module chips. The serial data are 8b/10b encoded, therefore the maximum data throughput is 960 Mb/s. The serial port can optionally operate at reduced line rates (600 Mb/s or 400 Mb/s).

The same interface is intended to be used for the transmission of data off-detector by the Outer Barrel Master chips, using a bit rate of 400 Mb/s (320 Mb/s payload). The Master chips also collect the data of a set of neighboring Outer Barrel Slave chips and forward their data off-detector on the differential link.

A bidirectional parallel data port with single-ended signaling is also present, with a capacity of  $320~\mathrm{Mb/s}$ . It enables the implementation of the data exchange between the Outer Barrel Slave chips and the corresponding Master. All the functionalities related to the communication between Master and Slave chips on the parallel bus are implemented in the module called Data Management Unit.

The ALPIDE chip has custom control interfaces. There is a differential control port (DCN-TRL) supporting bi-directional (half duplex) serial signaling at 40 Mb/s on differential links. A second single ended control line (CNTRL) is also available. These interfaces and the related control logic enable the interconnection of multiple chips on a multi-point control bus with a hierarchical topology, with control transactions relayed by the Master chips to Slave chips. The Control Management Unit block implements the control layer and provides full access to the control and status registers of the chip as well as to the multi-event memories in the Region Readout Units. The control bus is also used to distribute commands to the chips, most notably the trigger messages.

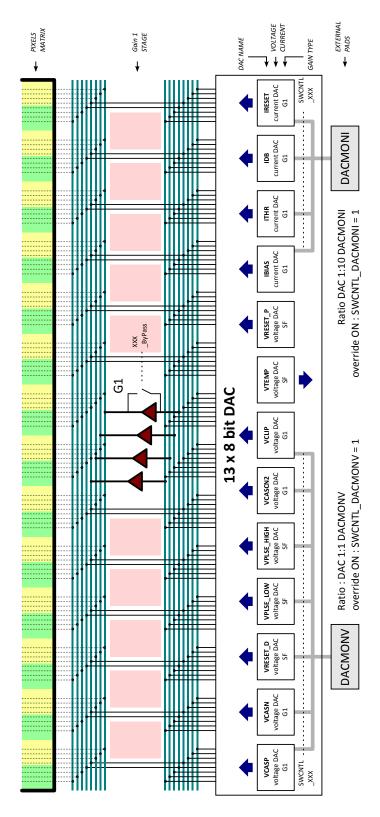

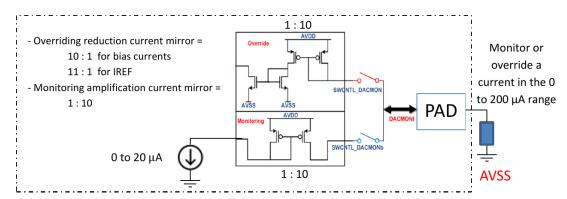

All the analog signals required by the front-ends are generated by a set of on-chip 8 bit DACs. Analog monitoring pads (DACMONV, DACMONI) are available to monitor the outputs of the internal DACs. The DACMONV pad can be used to override any of the voltage DACs. The DACMONI pad can be used to override any of the current DACs or to override the internal reference current used by the current DACs.

The analog section of the periphery also contains an ADC with 10-bit dynamic range, a bandgap voltage reference and a temperature sensing circuit. The ADC can be used to monitor several quasi-static internal analog signals: the outputs of the DACs, the analog and digital supply voltages, the bandgap voltage and the temperature sensor.

# 2 ALPIDE data sheet

# 2.1 Block diagrams

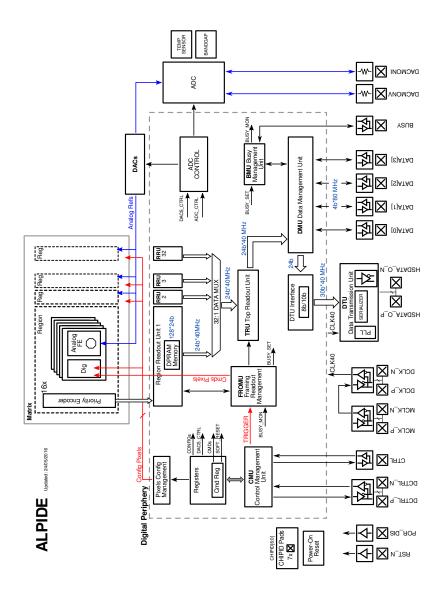

A general block diagram of the ALPIDE chip is given in Fig. 2.1.

A block diagram including details on the internal structures, module and peripheral hard blocks is given in Fig. 2.2.

Figure 2.1: ALPIDE chip block diagram.

# 2.2 Interface signals

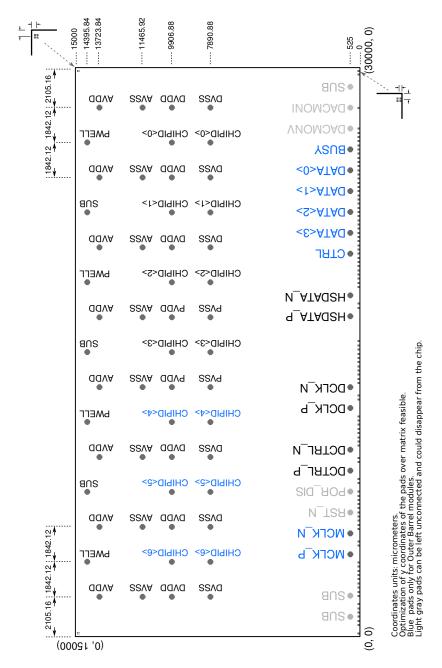

The main functional I/Os of the ALPIDE chip are listed in Table 2.1. Figure 2.3 shows the pinout of the chip with the locations of the pads.

The CMOS I/Os are 1.8 V compatible. Two types of CMOS I/O pad cells are used in ALPIDE: one has an internal pull-up resistor and one an internal pull-down resistor. The internal resistors are always connected to the pad. The driving strengths of the two cells are equal and fixed. The pad cells are tri-state capable and their drivers can be turned off and placed in a high-impedance mode depending on configuration and conditions. The internal pull-up or pull-down resistors remain connected and active in the high-impedance state.

The MCLK, DCTRL ans DCLK differential ports are implemented with a custom designed differential transceiver block. This has been designed with reference to standard TIA/EIA-899 Electrical Characteristics of Multipoint-Low-Voltage Differential Signaling (M-LVDS)<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> See Texas Instrument Application Report SLLA108A

Figure 2.2: ALPIDE chip block diagram with modules and peripheral hard-blocks.

However the differential ports are not standard compliant in particular with respect to the allowed range of the input common voltage.

Tables 2.3, Table 2.4 and Table 2.5 summarize the recommended DC operating conditions and the electrical characteristics of the various interfaces.

The analog monitoring ports provide access to internal nodes through a series resistor.

${\bf Table \ 2.1:} \ {\bf ALPIDE \ interface \ signals.}$

| Signal    | Type                   | Direction | Purpose                   |

|-----------|------------------------|-----------|---------------------------|

| MCLK_P    | Differential (MLVDS)   | INPUT     | Forwarded clock input     |

| MCLK_N    | Differential (MLVDS)   | INPUT     | Forwarded clock input     |

| RST_N     | CMOS, internal pull-up | INPUT     | Global chip reset         |

| POR_DIS_N | CMOS, internal pull-up | INPUT     | Power On Reset Disable    |

| DCTRL_P   | Differential (MLVDS)   | BIDIR     | Differential Control port |

| DCTRL_N   | Differential (MLVDS)   | BIDIR     | Differential Control port |

| DCLK_P    | Differential (MLVDS)   | BIDIR     | Main clock input          |

|           |                          |        | and clock forwarding output |

|-----------|--------------------------|--------|-----------------------------|

| DCLK_N    | Differential (MLVDS)     | BIDIR  | Main clock input            |

|           |                          |        | and clock forwarding output |

| HSDATA_P  | Differential (LVDS)      | OUTPUT | Serial Data Output          |

| HSDATA_N  | Differential (LVDS)      | OUTPUT | Serial Data Output          |

| CTRL      | CMOS, internal pull-up   | BIDIR  | Control port (OB local bus) |

| DATA[7]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[6]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[5]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[4]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[3]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[2]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[1]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| DATA[0]   | CMOS, internal pull-up   | BIDIR  | Data port (OB local bus)    |

| BUSY      | CMOS, internal pull-up   | BIDIR  | Busy flag                   |

| DACMONV   | ANALOG                   | OUTPUT | Voltage Monitoring Output   |

| DACMONI   | ANALOG                   | OUTPUT | Current Monitoring Output   |

| CHIPID[6] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[5] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[4] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[3] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[2] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[1] | CMOS, internal pull-down | INPUT  | Topological chip address    |

| CHIPID[0] | CMOS, internal pull-down | INPUT  | Topological chip address    |

MCLK\_P, MCLK\_N: Clock forwarding input port, used to implement the clock distribution in the Outer Barrel application scenario. This is a receiving only port, the driver behind it being disabled in all scenarios. The receiver is enabled when the chip is configured as Outer Barrel Master and the signal applied to this port is then forwarded to driver of the DCLK\_P, DCLK\_N port. A chip configured as Inner Chip or Outer Barrel slave chip keeps the receiver on this port disabled (refer to appendix A).

RST\_N: Global active-low reset signal. This port can be left unconnected in applications not needing a dedicated reset pin. The ALPIDE chip includes a power-on-reset circuit. The chip can also be reset by commands issued by the control interface.

**POR\_DIS\_N:** Disabling of the power-on-reset circuit, active low. Driving low this input masks the output of the internal power-on reset circuitry. If the internal power-on-reset is used this pin can be left unconnected since it is internally pulled-up.

**DCTRL\_P, DCTRL\_N:** Differential bidirectional control port. Intended to implement the segments of the control bus between the Inner Barrel chips or the Outer Barrel Master chips and the off detector electronics. The DCTRL port is unused by a chip configured as Outer Barrel Slave Chip. The communication through this port is half-duplex. Signals are received or driven but not simultaneously.

**DCLK\_P, DCLK\_N:** Main clock input and forwarded clock output. The nominal clock frequency is the LHC bunch frequency, 40.08 MHz. This is the chip clock source regardless of the operating mode and configuration scenario. In all configurations the receiver circuit at this port provides the clock to the chip core. A chip configured as Outer Barrel Master has an active driver on this port and forwards on it the signal received on the MCLK\_P, MCLK\_N port. This port is also equipped with an on-chip termination resistor (100  $\Omega$ ) that is enabled depending on the signals applied to the CHIPID configuration port. Additional details concerning the supported clocking schemes can be found in appendix A.

HSDATA\_P, HSDATA\_N: Differential data output port. This port is used for the high speed serial transmission of data between chips and the off-detector electronics. It is used by chips configured as Inner Barrel Chip or Outer Barrel Master. The signaling rate on this

Figure 2.3: Pinout of the ALPIDE chip.

port is programmable in the Inner Barrel Chip operating mode, selecting between 1.2 Gb/s (default), 600 Mb/s or 400 Mb/s. The signaling rate is 400 Mb/s in the Outer Barrel Master configuration. The serial stream is 8b/10b encoded.

CTRL: Single ended, bidirectional control port. Intended to implement the local control bus segments between the Outer Barrel Master chip and the associated slaves. These chips shall have their CTRL ports directly connected by a single shared wire. The CTRL port is unused by a chip configured as Inner Barrel Chip. The communication through this port is half-duplex. Signals are received or driven but not simultaneously.

**DATA**[7:0]: CMOS bidirectional data port. Intended to implement a shared parallel data bus between the Outer Barrel Slave chips and the associated Master chip. By default, the 4 lowermost lines of this port operate in Double Data Rate mode, with bits launched or sampled at both clock edges and one complete byte transfer completed at every clock cycle. Thus the uppermost 4 bits can be left unconnected and the bus can be implemented using 4 parallel wires shared by the chips. Optionally, the chips can be configured to revert to Single Data Rate signaling also on the lowermost 4 bits. In this case one byte is launched or sampled at every rising edge of the clock. This operating mode can be used for readout of chips through a 8 bit Single Data Rate parallel bus.

**BUSY:** Single ended port. It is intended to implement the communication of the BUSY state between the Outer Barrel Slaves and the associated Master chip by wiring in parallel all their BUSY ports. This port is not used when the chip operates as an ITS Inner Barrel chip. This port can be in one of two states: actively driven low or high impedance, thus emulating an open-drain topology. The signaling is active low. The pad provides weak internal pull-up. An external strong pull-up resistor might be required to speed-up the rise-time of the de-assertion (rising) edge depending on the total capacitance of the line and the number of chips connected to it. The sampling of the input on this port is equipped with a sychronizer.

**DACMONV:** Analog pin with dual functionality. It can be used to monitor each of the voltages generated by the on-chip voltage DACs. It can also be used to override the internal voltage DACs. The overriding is possible for one user-selectable DAC at a given time.

**DACMONI:** Analog pin with triple functionality. (a) Monitoring of the currents generated by the on-chip current DACs. (b) Override of the internal current DACs. The overriding is possible for one user-selectable DAC at a given time. (c) Override of the chip internal current reference, thus changing the range of all current DACs simultaneously.

CHIPID[6:0]: Chip topological address and mode selection. This port is intended to assign a binary coded address to each chip depending on its position on the ALICE ITS Modules. The address is used in the transactions via the control interface. The address value also selects if the chip behaves as a Inner Barrel Chip, an Outer Barrel Master chip or an Outer Barrel Slave chip. These pads have been designed to be directly wired to digital supply in order to set a binary '1' on intended lines. Leaving a pad unconnected effectively sets to '0' the corresponding input by the internal pull-down.

## 2.3 Supply, ground and bias nets

Table 2.2: ALPIDE supply, ground and bias nets.

| Net   | Type      | Purpose                           |

|-------|-----------|-----------------------------------|

| AVDD  | SUPPLY    | Analog domain supply              |

| AVSS  | GROUND    | Analog domain ground              |

| DVDD  | SUPPLY    | Digital domain supply             |

| DVSS  | GROUND    | Digital domain ground             |

| PVDD  | SUPPLY    | Data Transmission Unit PLL supply |

| PVSS  | GROUND    | Data Transmission Unit PLL ground |

| PWELL | SUBSTRATE | Substrate bias                    |

**AVDD**, **AVSS**: Supply and ground nets of the analog domain. This includes the pixel front-end circuits, the analog biasing circuits (DACs), the ADC block.

**DVDD, DVSS:** Supply and ground nets of the digital domain. This includes the in-pixel configuration registers, the matrix readout circuits, the peripheral readout circuits and the chip input and output buffers and transceivers.

**PDVDD, PDVSS:** Supply and ground nets exclusively dedicated to the Phase Locked Loop of the Data Transmission Unit.

**PWELL:** bias of the p-type wells in the pixel matrix region.

SUB: bias to the substrate contacts in the seal ring and in the periphery region.

All supply and ground nets must be connected to the recommended operating voltages. The pads of each supply or ground net are internally electrically connected by the on-chip supply and ground meshes. Therefore it is not mandatory to wire all the pads of a given supply or ground net. However, a reduction of the number of connected supply or ground pads can have detrimental effects on the circuit performance and operating capabilities or increase the risk of damaging the chip.

The PWELL and SUB bias nets cannot be left floating and must be strongly connected to appropriate bias voltages. The source impedance of the supply to these nets shall be kept as low as possible to limit the probability of latch-up.

The pads of the PWELL net are internally connected as well as those of the SUB net, therefore it is not mandatory to wire all the pads of a given net. The PWELL and SUB nets are electrically connected to each other through the conductance of the die substrate.

The purpose of the PWELL and SUB substrate biasing nets is to enable the increase of the reverse bias voltage on the charge collecting diodes. This is obtained by applying to these nets a negative voltage with respect to analog ground (AVSS). For applications not demanding enhanced sensor performance it is possible to short both the PWELL and SUB pads to the AVSS ground (0 V with respect to AVSS).

It is recommended to bond the PWELL and SUB pads to a grounding conductor before any other pad is bonded, to mitigate the risk of ESD damage.

# 2.4 Recommended operating conditions

MIN TYPMAX Unit Condition AVSS Analog ground 0 V AVDD 1.8 V Analog supply 1.62 1.98 DVSS Digital core ground V DVDD Digital core supply 1.62 1.8 1.98 V PVSS PLL ground 0 V **PVDD** PLL supply 1.62 1.8 V 1.98 **PWELL** V Substrate bias -6 0 SUB Substrate bias -6 0 V Voltage at any CMOS input DVDD V  $\overline{V_{I}}$ 0 0.33\*DVDD V  $V_{\rm IL}$ Low level digital input voltage  $V_{IH}$ High level digital 0.66\*DVDD V input voltage  $I_{\rm OL}$ Low level digital 13.7(?) mAVo < 0.45output current  $|I_{OH}|$ High level digital 13.6(?) mA $\mathrm{Vo}>\!\mathrm{DVDD}\text{-}0.45$

Table 2.3: Recommended operating conditions.

|                                  | output current               |        |       |                     |                      |  |

|----------------------------------|------------------------------|--------|-------|---------------------|----------------------|--|

| V <sub>P</sub> or V <sub>N</sub> | Voltage at any               | 0      |       | DVDD                | V                    |  |

|                                  | differential bus terminal    |        |       |                     |                      |  |

| $ V_{ID} $                       | Magnitude of                 | 50     |       | DVDD                | mV                   |  |

|                                  | differential input voltage   |        |       |                     |                      |  |

| $R_{L}$                          | Differential load resistance | 40 (?) | 50(?) | 60 <mark>(?)</mark> | Ω                    |  |

| Т                                | Operating temperature        | -25    | 25    | 85                  | $^{\circ}\mathrm{C}$ |  |

# 2.5 Electrical characteristics

Table 2.4: CMOS IOs electrical characteristics over recommended operating conditions unless otherwise noted

|                 |                          | MIN       | TYP  | MAX  | Unit      | Condition                     |

|-----------------|--------------------------|-----------|------|------|-----------|-------------------------------|

| V <sub>OH</sub> | High level               | DVDD-0.45 |      |      | V         | Io >-13.6 mA                  |

|                 | output voltage           |           |      |      |           |                               |

| $V_{OL}$        | Low level                |           |      | 0.45 | V         | Io < 13.7  mA                 |

|                 | output voltage           |           |      |      |           |                               |

| $ I_{IL} $      |                          |           | 44.4 | 62   | $\mu$ A   | Pads with pull-up             |

| $I_{IH}$        |                          |           | 0.87 | 3.8  | nA        | Pads with pull-up             |

| $ I_{IL} $      |                          |           | 3.3  | 11.5 | nA        | Pads with pull-down           |

| $I_{IH}$        |                          |           | 44.4 | 62   | $\mu$ A   | Pads with pull-down           |

| $R_{Pullup}$    | Internal pull-up         |           | 40.6 |      | $k\Omega$ | Pads with pull-up             |

| $R_{Pullup}$    | Internal pull-down       |           | 40.6 |      | $k\Omega$ | Pads with pull-down           |

| $C_{PAD}$       | Input capacitance        |           | 0.98 |      | pF        | Inputs with A type pad only   |

| $C_{PAD}$       | Input capacitance        |           | 4.5  |      | pF        | Inputs with A and B type pads |

| $R_s$           | Output series resistance |           | (?)  |      | Ω         |                               |

Table 2.5: Electrical characteristics of MCLK, DCTRL and DCLK differential ports over recommended operating conditions unless otherwise noted.

|                                  |                             | MIN            | TYP | MAX     | Unit          | Condition           |

|----------------------------------|-----------------------------|----------------|-----|---------|---------------|---------------------|

| C <sub>P</sub> or C <sub>N</sub> | Input capacitance           |                |     | 3       | pF            | $V_{I}$ ,           |

|                                  |                             |                |     |         |               | other pin at 1.1 V, |

|                                  |                             |                |     |         |               | driver disabled     |

| $C_{PN}$                         | Differential input          |                |     |         | pF            | $V_{ID} =$ ,        |

|                                  | capacitance                 |                |     |         |               | $V_{IC} =$ ,        |

|                                  |                             |                |     |         |               | driver disabled     |

| $I_{OZ}$                         | High-impedance state        | -45            |     | 102     | $\mu$ A       | Driver disabled     |

|                                  | output current              |                |     |         |               |                     |

|                                  | Driv                        | ver related ch |     |         |               |                     |

|                                  |                             | MIN            | TYP | MAX     | Unit          | Condition           |

| $ V_{OD} $                       | Output differential         | 80 (?)         |     | 480(?)  | $\mathrm{mV}$ |                     |

|                                  | signal magnitude            |                |     |         |               |                     |

| $ I_{OD} $                       | Output differential         | 2              |     | 8       | mA            |                     |

|                                  | current magnitude           |                |     |         |               |                     |

| $V_{OS(SS)}$                     | Steady-state output         | 980            |     | 1210    | $\mathrm{mV}$ |                     |

|                                  | common signal               |                |     |         |               |                     |

| $\Delta V_{OS(SS)}$              | Change in steady-state      | -20            |     | +20     | mV            |                     |

|                                  | output common signal        |                |     |         |               |                     |

|                                  | between logic states        |                |     |         |               |                     |

| $V_{OS(PP)}$                     | Peak-to-peak output         |                |     | 75      | mV            |                     |

|                                  | common signal               |                |     |         |               |                     |

|                                  | Rece                        | iver related c |     |         |               |                     |

|                                  |                             | MIN            | TYP | MAX     | Unit          | Condition           |

| $V_{IC}$                         | Input common signal         | DVSS+25        | 1.1 | DVDD-25 | mV            |                     |

| $V_{IT+}$                        | Positive-going differential |                |     | 50      | $\mathrm{mV}$ |                     |

|                                  | input voltage threshold     |                |     |         |               |                     |

| $ V_{IT-} $                      | Negative-going differential | -50            |     |         | mV            |                     |

| t voltage threshold |  |

|---------------------|--|

# 2.6 Pad tables, geometrical data, alignment markers

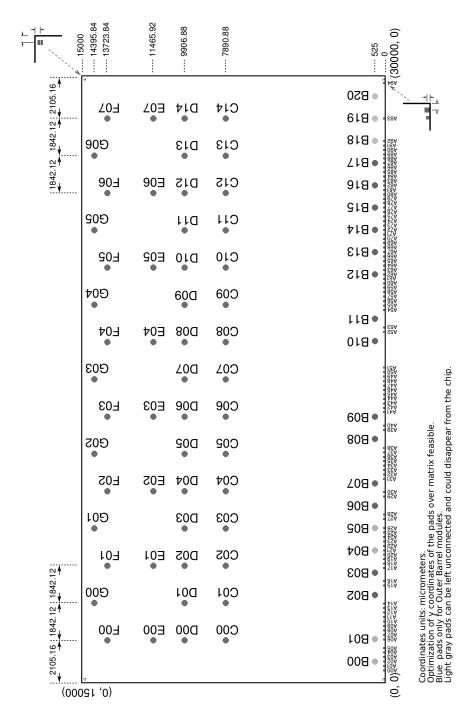

A floorplan view with the name of the pad nets at the pads used for the connection to the ALICE ITS FPCs is given in Figure 2.3. The pad naming convention and the layout of the die with the position of the pads are illustrated in Figure 2.4.

Table 2.6 lists all the pads and interface nets of the chip. Table 2.7 gives the x and y coordinates of the *center* points of the chip pads.

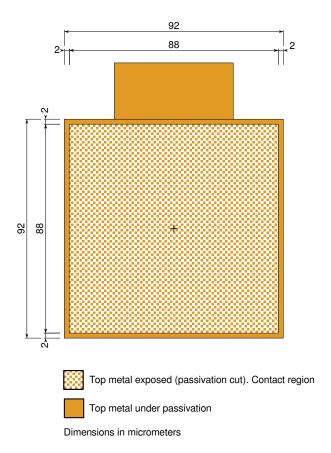

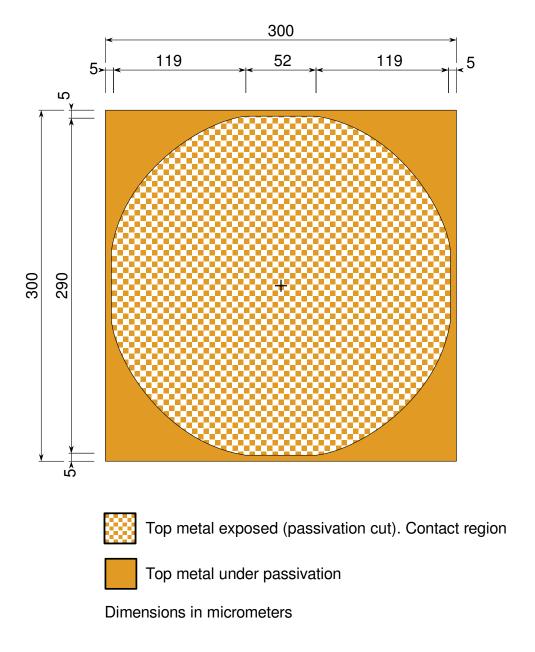

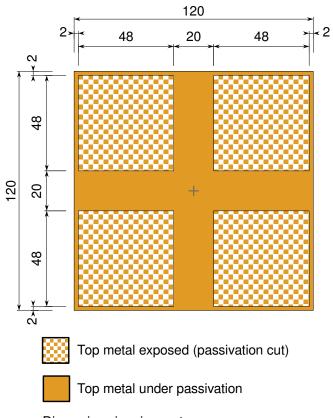

Two types of pads with differing geometries are employed in the ALPIDE chip.

Type A pads are used for the pads in the pad ring along the chip south edge (from A00 to A94). All interface nets are available in this pad ring. Type A pads are standard size and intended to support wire bonding, probe testing or other applications. Figure 2.5 details the geometry of the opening of type A pads. The opening in the passivation layer of type A pads is square and 88  $\mu$ m wide.

Type B are large pads over logic used above the periphery and the sensitive matrix of the chip (B00-B20, C00-C14, D00-D14, E00-E07, F00-F07, G00-G06). These pads enable the connection to Flexible Printed Circuits. The nets accessible through pads of type B are also found in the ring of pads of type A. Figure 2.6 details the geometry of the opening of pads of type B. The opening in the passivation layer of type B pads has rounded edges and it is 290  $\mu$ m wide.

The chip includes four structures located close to the four corners of the die to facilitate geometrical alignment procedures, as shown in Figure 2.4 for the markers on the top-right and bottom-right corners. Figure 2.7 details the geometry of the alignment markers. The coordinates of the central point of the alignment markers are listed in table 2.8.

Table 2.6: ALPIDE pads and interface nets.

| Pad Id | Net          | Type            | Direction | Purpose                   |

|--------|--------------|-----------------|-----------|---------------------------|

| A00    | PWELL        | SUBSTRATE       |           | Substrate bias, Matrix    |

| A01    | AVSS         | GROUND          |           | Analog ground             |

| A02    | SUB          | SUBSTRATE       |           | Substrate bias, periphery |

| A03    | AVDD         | SUPPLY          |           | Analog supply             |

| A04    | DVSS         | GROUND          |           | Digital ground            |

| A05    | DVDD         | SUPPLY          |           | Digital supply            |

| A06    | SUB          | SUBSTRATE       |           | Substrate bias, periphery |

| A07    | AVSS         | GROUND          |           | Analog ground             |

| A08    | AVDD         | SUPPLY          |           | Analog supply             |

| A09    | DVSS         | GROUND          |           | Digital ground            |

| A10    | DVDD         | SUPPLY          |           | Digital supply            |

| A11    | SCI          | CMOS            |           | Unused                    |

| A12    | AVSS         | GROUND          |           | Analog ground             |

| A13    | AVDD         | SUPPLY          |           | Analog supply             |

| A14    | CHIPID[6]    | CMOS, pull-down | INPUT     | Topological chip address  |

| A15    | $MCLK_P$     | MLVDS           | INPUT     | Forwarded clock input     |

| A16    | $MCLK_N$     | MLVDS           | INPUT     | Forwarded clock input     |

| A17    | DVSS         | GROUND          |           | Digital ground            |

| A18    | DVDD         | SUPPLY          |           | Digital supply            |

| A19    | PWELL        | SUBSTRATE       |           | Substrate bias, Matrix    |

| A20    | $RESERVE\_0$ | CMOS            |           | Unused                    |

| A21    | $RST_N$      | CMOS, pull-up   | INPUT     | Global Hard Reset         |

| A22    | $RESERVE_2$  | CMOS            |           | Unused                    |

| A23    | DVSS         | GROUND          |           | Digital ground            |

| A24    | DVDD         | SUPPLY          |           | Digital supply            |

| A25    | CHIPID[5]    | CMOS, pull-down | INPUT     | Topological chip address  |

| A26    | POR_DIS_N    | CMOS, pull-up   | INPUT     | Disable Power-On Reset    |

| A27    | AVSS         | GROUND          |           | Analog ground             |

| A28    | AVDD         | SUPPLY          |           | Analog supply             |

| A29    | DCTRL_P      | MLVDS           | BIDIR     | Differential Control port |

| A30    | DCTRL_N      | MLVDS           | BIDIR     | Differential Control port |

| A31    | DVSS         | GROUND          |           | Digital ground            |

| A32    | DVDD         | SUPPLY          |           | Digital supply            |

| A33    | SUB          | SUBSTRATE       |           | Substrate bias, periphery |

| A34    | AVSS         | GROUND          |           | Analog ground             |

| 1 40=      | 11777             | Larranti                  |          |                                         |

|------------|-------------------|---------------------------|----------|-----------------------------------------|

| A35        | AVDD              | SUPPLY                    |          | Analog supply                           |

| A36        | SCO               | CMOS                      | INIDITE  | Unused                                  |

| A37        | CHIPID[4]         | CMOS, pull-down           | INPUT    | Topological chip address                |

| A38        | DVSS              | GROUND                    | DIDID    | Digital ground                          |

| A39        | DCLK_P            | MLVDS                     | BIDIR    | Clock input. Clock forwarding output    |

| A40        | DCLK_N            | MLVDS                     | BIDIR    | Clock input. Clock forwarding output    |

| A41        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A42        | PWELL             | SUBSTRATE                 |          | Substrate bias, Matrix                  |

| A43        | DVSS              | GROUND                    |          | Digital ground                          |

| A44        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A45        | AVSS              | GROUND                    |          | Analog ground                           |

| A46        | AVDD              | SUPPLY                    | DIDITE   | Analog supply                           |

| A47        | CHIPID[3]         | CMOS, pull-down           | INPUT    | Topological chip address                |

| A48        | PVSS              | GROUND                    |          | PLL ground                              |

| A49        | PVDD              | SUPPLY                    |          | PLL supply                              |

| A50        | PVSS              | GROUND                    |          | PLL ground                              |

| A51        | PVDD              | SUPPLY                    | OHEDHE   | PLL supply<br>Serial Data Port          |

| A52        | HSDATA_P          | LVDS                      | OUTPUT   | 12 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  |

| A53        | HSDATA_N<br>DVDD  | LVDS                      | OUTPUT   | Serial Data Port                        |

| A54<br>A55 |                   | SUPPLY CMOS pull down     | INPUT    | Digital supply Topological chip address |

| A56        | CHIPID[2]<br>DVSS | CMOS, pull-down<br>GROUND | TIVE U I | Digital ground                          |

| A50<br>A57 | SCE               | CMOS                      |          | Unused                                  |

| A57<br>A58 | AVSS              | GROUND                    |          | Analog ground                           |

| A59        | AVDD              | SUPPLY                    |          | Analog ground<br>Analog supply          |

| A60        | DVSS              | GROUND                    |          | Digital ground                          |

| A61        | DVDD              | SUPPLY                    |          | Digital ground Digital supply           |

| A62        | CTRL              | CMOS, pull-up             | BIDIR    | Control Port (OB)                       |

| A63        | DVSS              | GROUND                    | DIDII(   | Digital ground                          |

| A64        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A65        | DVSS              | GROUND                    |          | Digital ground                          |

| A66        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A67        | DATA[3]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A68        | DATA[7]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A69        | DVSS              | GROUND                    |          | Digital ground                          |

| A70        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A71        | CHIPID[1]         | CMOS, pull-down           | INPUT    | Topological chip address                |

| A72        | DATA[2]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A73        | DATA[6]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A74        | DVSS              | GROUND                    |          | Digital ground                          |

| A75        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A76        | DVSS              | GROUND                    |          | Digital ground                          |

| A77        | DATA[1]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A78        | DATA[5]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A79        | DVDD              | SUPPLY                    |          | Digital supply                          |

| A80        | AVSS              | GROUND                    |          | Analog ground                           |

| A81        | AVDD              | SUPPLY                    |          | Analog supply                           |

| A82        | DATA[0]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A83        | DATA[4]           | CMOS, pull-up             | BIDIR    | Data port                               |

| A84        | SUB               | SUBSTRATE                 |          | Substrate bias, periphery               |

| A85        | DVSS              | GROUND                    |          | Digital ground                          |

| A86        | DVDD              | SUPPLY                    | D.T      | Digital supply                          |

| A87        | BUSY              | CMOS, pull-up             | BIDIR    | Busy Flag                               |

| A88        | CHIPID[0]         | CMOS, pull-down           | INPUT    | Topological chip address                |

| A89        | AVSS              | GROUND                    |          | Analog ground                           |

| A90        | AVDD              | SUPPLY                    |          | Analog supply                           |

| A91        | PWELL             | SUBSTRATE                 |          | Substrate bias, Matrix                  |

| A92        | DACMONV           | ANALOG                    |          | Voltage monitoring and overriding       |

| A93        | DACMONI           | ANALOG                    |          | Current monitoring and overriding       |

| A94        | SUB               | SUBSTRATE                 |          | Substrate bias, periphery               |

|            |                   | I                         |          |                                         |

| B00 | SUB        | SUBSTRATE       |            | Substrate bias, periphery             |

|-----|------------|-----------------|------------|---------------------------------------|

| B01 | SUB        | SUBSTRATE       |            | Substrate bias, periphery             |

| B02 | MCLKP      | MLVDS           | INPUT      | Forwarded clock input                 |

| B03 | $MCLK_N$   | MLVDS           | INPUT      | Forwarded clock input                 |

| B04 | $RST_N$    | CMOS, pull-up   | INPUT      | Global Hard Reset                     |

| B05 | POR_DIS_N  | CMOS, pull-up   | INPUT      | Disable Power-On Reset                |

| B06 | DCTRL_P    | MLVDS           | BIDIR      | Differential Control port             |

| B07 |            | MLVDS           | BIDIR      | *                                     |

| 1   | DCTRL_N    |                 |            | Differential Control port             |

| B08 | DCLK_P     | MLVDS           | BIDIR      | Clock input. Clock forwarding output  |

| B09 | DCLK_N     | MLVDS           | BIDIR      | Clock input. Clock forwarding output  |

| B10 | HSDATA_P   | LVDS            | OUTPUT     | Serial Data Port                      |

| B11 | $HSDATA_N$ | LVDS            | OUTPUT     | Serial Data Port                      |

| B12 | CTRL       | CMOS, pull-up   | BIDIR      | Control Port (OB)                     |

| B13 | DATA[3]    | CMOS, pull-up   | BIDIR      | Data port                             |

| B14 | DATA[2]    | CMOS, pull-up   | BIDIR      | Data port                             |

| B15 | DATA[1]    | CMOS, pull-up   | BIDIR      | Data port                             |

| B16 | DATA[0]    | CMOS, pull-up   | BIDIR      | Data port                             |

| B17 | BUSY       | CMOS, pull-up   | BIDIR      | Busy Flag                             |

| B18 | DACMONI    | ANALOG          | וועונע     | Current monitoring and overriding     |

| 1   |            |                 |            |                                       |

| B19 | DACMONV    | ANALOG          |            | Voltage monitoring and overriding     |

| B20 | SUB        | SUBSTRATE       |            | Substrate bias, periphery             |

| C00 | DVSS       | GROUND          |            | Digital ground                        |

| C01 | CHIPID[6]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C02 | DVSS       | GROUND          | 1111 01    | Digital ground                        |

| C02 | CHIPID[5]  | CMOS, pull-down | INPUT      | Topological chip address              |

| 1   | • •        |                 | INFUI      |                                       |

| C04 | DVSS       | GROUND          | TAIDIIT    | Digital ground                        |

| C05 | CHIPID[4]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C06 | PVSS       | GROUND          |            | PLL ground                            |

| C07 | CHIPID[3]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C08 | PVSS       | GROUND          |            | PLL ground                            |

| C09 | CHIPID[2]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C10 | DVSS       | GROUND          |            | Digital ground                        |

| C11 | CHIPID[1]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C12 | DVSS       | GROUND          |            | Digital ground                        |

| C13 | CHIPID[0]  | CMOS, pull-down | INPUT      | Topological chip address              |

| C14 | DVSS       | GROUND          | 11.11 () 1 | Digital ground                        |

| 011 | 2,00       | 0100 0112       |            | 2 given ground                        |

| D00 | DVDD       | SUPPLY          |            | Digital supply                        |

| D01 | CHIPID[6]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D02 | DVDD       | SUPPLY          |            | Digital supply                        |

| D03 | CHIPID[5]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D04 | DVDD       | SUPPLY          |            | Digital supply                        |

| D05 | CHIPID[4]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D05 | PVDD       | SUPPLY          | 11.11 () 1 | PLL supply                            |

| 1   |            |                 | INDIT      |                                       |

| D07 | CHIPID[3]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D08 | PVDD       | SUPPLY          | INIDIE     | PLL supply                            |

| D09 | CHIPID[2]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D10 | DVDD       | SUPPLY          |            | Digital supply                        |

| D11 | CHIPID[1]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D12 | DVDD       | SUPPLY          |            | Digital supply                        |

| D13 | CHIPID[0]  | CMOS, pull-down | INPUT      | Topological chip address              |

| D14 | DVDD       | SUPPLY          |            | Digital supply                        |

| EOO | ATTOO      | CDOUND          |            | A 1 1                                 |

| E00 | AVSS       | GROUND          |            | Analog ground                         |

| E01 | AVSS       | GROUND          |            | Analog ground                         |

| E02 | AVSS       | GROUND          |            | Analog ground                         |

| E03 | AVSS       | GROUND          |            | Analog ground                         |

| E04 | AVSS       | GROUND          |            | Analog ground                         |

| E05 | AVSS       | GROUND          |            | Analog ground                         |

| E06 | AVSS       | GROUND          |            | Analog ground                         |

| 1   |            | f.              |            | · · · · · · · · · · · · · · · · · · · |

| E07 | AVSS    | GROUND    | Analog ground             |

|-----|---------|-----------|---------------------------|

| F00 | AVDD    | SUPPLY    | Analog supply             |

| F01 | AVDD    | SUPPLY    | Analog supply             |

| F02 | AVDD    | SUPPLY    | Analog supply             |

| F03 | AVDD    | SUPPLY    | Analog supply             |

| F04 | AVDD    | SUPPLY    | Analog supply             |

| F05 | AVDD    | SUPPLY    | Analog supply             |

| F06 | AVDD    | SUPPLY    | Analog supply             |

| F07 | AVDD    | SUPPLY    | Analog supply             |

|     |         |           |                           |

| G00 | ) PWELL | SUBSTRATE | Substrate bias, Matrix    |

| G01 | l SUB   | SUBSTRATE | Substrate bias, periphery |

| G02 | 2 PWELL | SUBSTRATE | Substrate bias, Matrix    |

| G03 | 3 SUB   | SUBSTRATE | Substrate bias, periphery |

| G04 | 4 PWELL | SUBSTRATE | Substrate bias, Matrix    |

| G05 | 5 SUB   | SUBSTRATE | Substrate bias, periphery |

| G06 | 6 PWELL | SUBSTRATE | Substrate bias, Matrix    |

Table 2.7: Coordinates of the center points of the pads.

| Pad Id | Net            | Pad Geometry | x [μm]   | y [μm] |

|--------|----------------|--------------|----------|--------|

| A00    | PWELL          | A            | 607.62   | 66.8   |

| A01    | AVSS           | A            | 827.62   | 66.8   |

| A02    | SUB            | A            | 1047.62  | 66.8   |

| A03    | AVDD           | A            | 1267.62  | 66.8   |

| A04    | DVSS           | A            | 1487.62  | 66.8   |

| A05    | DVDD           | A            | 1707.62  | 66.8   |

| A06    | SUB            | A            | 2147.62  | 66.8   |

| A07    | AVSS           | A            | 2367.62  | 66.8   |

| A08    | AVDD           | A            | 2587.62  | 66.8   |

| A09    | DVSS           | A            | 2807.62  | 66.8   |

| A10    | DVDD           | A            | 3027.62  | 66.8   |

| A11    | SCI            | A            | 3247.62  | 66.8   |

| A12    | AVSS           | A            | 3467.62  | 66.8   |

| A13    | AVDD           | A            | 3687.62  | 66.8   |

| A14    | CHIPID[6]      | A            | 3907.62  | 66.8   |

| A15    | $MCLK_P$       | A            | 4797.62  | 62.755 |

| A16    | $MCLK_N$       | A            | 5017.62  | 62.755 |

| A17    | DVSS           | A            | 5667.62  | 66.8   |

| A18    | DVDD           | A            | 5887.62  | 66.8   |

| A19    | PWELL          | A            | 6107.62  | 66.8   |

| A20    | RESERVE_0      | A            | 6327.62  | 66.8   |

| A21    | $RST_N$        | A            | 6547.62  | 66.8   |

| A22    | $RESERVE_{-2}$ | A            | 6767.62  | 66.8   |

| A23    | DVSS           | A            | 6987.62  | 66.8   |

| A24    | DVDD           | A            | 7207.62  | 66.8   |

| A25    | CHIPID[5]      | A            | 7427.62  | 66.8   |

| A26    | POR_DIS_N      | A            | 7647.62  | 66.8   |

| A27    | AVSS           | A            | 8087.62  | 66.8   |

| A28    | AVDD           | A            | 8307.62  | 66.8   |

| A29    | $DCTRL_P$      | A            | 9197.62  | 62.755 |

| A30    | $DCTRL_N$      | A            | 9417.62  | 62.755 |

| A31    | DVSS           | A            | 10067.62 | 66.8   |

| A32    | DVDD           | A            | 10287.62 | 66.8   |

| A33    | SUB            | A            | 10507.62 | 66.8   |

| A34    | AVSS           | A            | 10727.62 | 66.8   |

| A35    | AVDD           | A            | 10947.62 | 66.8   |

| A36    | SCO            | A            | 11167.62 | 66.8   |

| A37    | CHIPID[4]      | A            | 11387.62 | 66.8   |

| A38        | DVSS          | A      | 11607.62                              | 66.8   |

|------------|---------------|--------|---------------------------------------|--------|

| A39        | $DCLK_P$      | A      | 12497.62                              | 62.755 |

| A40        | $DCLK_N$      | A      | 12717.62                              | 62.755 |

| A41        | DVDD          | A      | 13367.62                              | 66.8   |

| A42        | PWELL         | A      | 13587.62                              | 66.8   |

| A43        | DVSS          | A      | 13807.62                              | 66.8   |

| A44        | DVDD          | A      | 14027.62                              | 66.8   |

| A44<br>A45 | AVSS          | A      | 14027.02                              | 66.8   |

|            |               | A      |                                       |        |

| A46        | AVDD          | 1      | 14467.62                              | 66.8   |

| A47        | CHIPID[3]     | A      | 14687.62                              | 66.8   |

| A48        | PVSS          | A      | 14907.62                              | 66.8   |

| A49        | PVDD          | A      | 15127.62                              | 66.8   |

| A50        | PVSS          | A      | 15347.62                              | 66.8   |

| A51        | PVDD          | A      | 15567.62                              | 66.8   |

| A52        | $HSDATA_{-}P$ | A      | 17325.355                             | 61.82  |

| A53        | $HSDATA_N$    | A      | 17545.355                             | 61.82  |

| A54        | DVDD          | A      | 18427.62                              | 66.8   |

| A55        | CHIPID[2]     | A      | 18647.62                              | 66.8   |

| A56        | DVSS          | A      | 18867.62                              | 66.8   |

| A57        | SCE           | A      | 19087.62                              | 66.8   |

| A58        | AVSS          | A      | 19307.62                              | 66.8   |

| A59        | AVDD          | A      | 19527.62                              | 66.8   |

| A60        | DVSS          | A      | 19747.62                              | 66.8   |

| A61        | DVSS          | A      | 19747.62                              | 66.8   |

|            |               |        |                                       | 66.8   |

| A62        | CTRL          | A      | 20187.62                              |        |

| A63        | DVSS          | A      | 20407.62                              | 66.8   |

| A64        | DVDD          | A      | 20627.62                              | 66.8   |

| A65        | DVSS          | A      | 20847.62                              | 66.8   |

| A66        | DVDD          | A      | 21067.62                              | 66.8   |

| A67        | DATA[3]       | A      | 21287.62                              | 66.8   |

| A68        | DATA[7]       | A      | 21507.62                              | 66.8   |

| A69        | DVSS          | A      | 21727.62                              | 66.8   |

| A70        | DVDD          | A      | 21947.62                              | 66.8   |

| A71        | CHIPID[1]     | A      | 22167.62                              | 66.8   |

| A72        | DATA[2]       | A      | 22387.62                              | 66.8   |

| A73        | DATA[6]       | A      | 22607.62                              | 66.8   |

| A74        | DVSS          | A      | 22827.62                              | 66.8   |

| A75        | DVDD          | A      | 23047.62                              | 66.8   |

| A76        | DVSS          | A      | 23267.62                              | 66.8   |

| A77        | DATA[1]       | A      | 23487.62                              | 66.8   |

| A78        | DATA[5]       | A      | 23707.62                              | 66.8   |

| A79        | DVDD          | A      | 23927.62                              | 66.8   |

|            | AVSS          | A      |                                       |        |

| A80        | AV SS<br>AVDD | A<br>A | 24147.62                              | 66.8   |

| A81        |               |        | 24367.62                              | 66.8   |

| A82        | DATA[0]       | A      | 24587.62                              | 66.8   |

| A83        | DATA[4]       | A      | 24807.62                              | 66.8   |

| A84        | SUB           | A      | 25027.62                              | 66.8   |

| A85        | DVSS          | A      | 25247.62                              | 66.8   |

| A86        | DVDD          | A      | 25467.62                              | 66.8   |

| A87        | BUSY          | A      | 25687.62                              | 66.8   |

| A88        | CHIPID[0]     | A      | 25907.62                              | 66.8   |

| A89        | AVSS          | A      | 26127.62                              | 66.8   |

| A90        | AVDD          | A      | 26347.62                              | 66.8   |

| A91        | PWELL         | A      | 26567.62                              | 66.8   |

| A92        | DACMONV       | A      | 26797.62                              | 66.8   |

| A93        | DACMONI       | A      | 27897.62                              | 66.8   |

| A94        | SUB           | A      | 29627.62                              | 66.8   |

|            | ~             |        | ===================================== | 33.0   |

| B00        | SUB           | В      | 1057.62                               | 525    |

| B01        | SUB           | В      | 2157.62                               | 525    |

| B02        | MCLK_P        | В      | 4357.62                               | 525    |

| D02        | MIOTIV_L      | р      | 1001.02                               | 929    |

| B03  | $MCLK_N$   | В | 5457.62  | 525      |

|------|------------|---|----------|----------|

| B04  | RST_N      | В | 6557.62  | 525      |

| 1    |            |   |          |          |

| B05  | POR_DIS_N  | В | 7657.62  | 525      |

| B06  | $DCTRL_P$  | В | 8757.62  | 525      |

|      | DCTRL_N    |   |          |          |

| B07  |            | В | 9857.62  | 525      |

| B08  | $DCLK_P$   | В | 12057.62 | 525      |