Hardware Documentation and Howto's: Difference between revisions

From pCT

| Line 43: | Line 43: | ||

=== Transition Card === | === Transition Card === | ||

=== ALPIDE Chip === | |||

* [[Media:alpide_manual_ver3.pdf | ALPIDE Manual v0.3]] | |||

=== ALPIDE Bonding and Mounting === | === ALPIDE Bonding and Mounting === | ||

Revision as of 09:29, 13 September 2019

Getting Started

Documentation

pRU

pRU Registers and Bus System

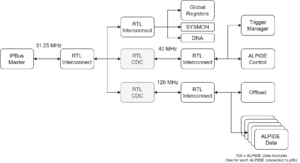

The pRU bus system is connecting the various modules on the FPGA to a common master, the Microblaze Subsystem. Each of the modules is associated with a given BASE-ADDRESS specified in the pRU Control Interface Document. Note that several instances do exist for certain modules. E.g. there are one alpide_data instance for each ALPIDE chip connected to the pRU. To communicate with a specific instance one needs to add an offset of 0x1000 times the instance number to the module base address.

E.g. if you want to communicate with the

- 1st instance: <ALPIDE_DATA_BASEADDR>

- 2nd instance: <ALPIDE_DATA_BASEADDR> + (0x1000 * 2-1)

- 16th instance: <ALPIDE_DATA_BASEADDR> + (0x1000 * 16-1)

Module Registers

- global_regs

- trigger_manager

- offload documentation is coming when latest pDTP status registers are added

- alpide_control

- alpide_data