Hardware Documentation and Howto's: Difference between revisions

From pCT

| Line 67: | Line 67: | ||

* [[:Media:2019_11_05.zip | 2019 November 5 ]] | * [[:Media:2019_11_05.zip | 2019 November 5 ]] | ||

* Some of the aluminium traces on the flex cable broke by the tail of the cable (near the ZIF stiffener). [[ | * Some of the aluminium traces on the flex cable broke by the tail of the cable (near the ZIF stiffener). [[Media:Tail_modifications.png | Current design and possible modifications]] shows the current design and two possible modifications. It has been decided that new designs will use the design 1 modification and longer ZIF-stiffener (30 mm long). | ||

=== Production Test Box (PTB) === | === Production Test Box (PTB) === | ||

Revision as of 14:03, 10 January 2022

Main Page -> Hardware Documentation and Howto's

Getting Started

Documentation

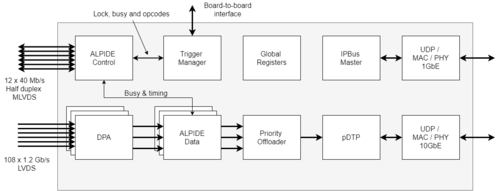

pRU

- pRU Clock Network

- pRU Address Map

- DCS and Data Offload Ethernet Configurations

- pCT Data Transfer Protocol

- pRU Data Format

- FPGA and ALPIDE radiation calculations

- pRU Control Interface [Deprecated, only in use on PTB. Replaced with IPBus on VCU118 + all other boards in the future.]

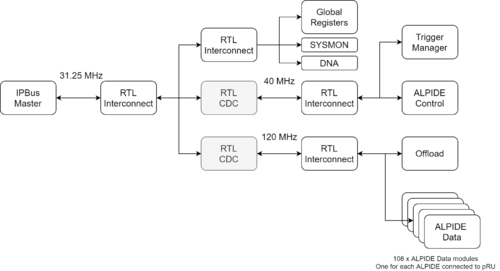

pRU Registers and Bus System

The pRU bus system is connecting the various modules on the FPGA to a common master, the Microblaze Subsystem. Each of the modules is associated with a given BASE-ADDRESS specified in the pRU Control Interface Document. Note that several instances do exist for certain modules. E.g. there are one alpide_data instance for each ALPIDE chip connected to the pRU. To communicate with a specific instance one needs to add an offset of 0x1000 times the instance number to the module base address.

E.g. if you want to communicate with the

- 1st instance: <ALPIDE_DATA_BASEADDR>

- 2nd instance: <ALPIDE_DATA_BASEADDR> + (0x1000 * (2-1))

- 16th instance: <ALPIDE_DATA_BASEADDR> + (0x1000 * (16-1))

Module Registers

PTB-specific Module Registers

Transition Card (TC)

ALPIDE Chip

ALPIDE Bonding and Mounting

Chip Cable

9 Chip String

- 2019 November 5

- Some of the aluminium traces on the flex cable broke by the tail of the cable (near the ZIF stiffener). Current design and possible modifications shows the current design and two possible modifications. It has been decided that new designs will use the design 1 modification and longer ZIF-stiffener (30 mm long).

Production Test Box (PTB)

FPGA Mezzanine Card (FMC)

mTower

Cooling Laboratory Setup

LAUDA Ultracool UC 4 is used for water cooling in the laboratory now (data sheet and manual).